# ispXPLD<sup>™</sup> 5000MX Family

3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD<sup>™</sup> Family

#### July 2002

#### **Features**

- Flexible Multi-Function Block (MFB) Architecture

- SuperWIDE<sup>™</sup> logic (up to 136 inputs)

- Arithmetic capability

- · Single- or Dual-port SRAM

- FIFO

- Ternary CAM

#### ■ sysCLOCK<sup>™</sup> PLL Timing Control

- Multiply and divide between 1 and 32

- Clock shifting capability

- External feedback capability

#### ■ sysIO<sup>™</sup> Interfaces

- LVCMOS 1.8, 2.5, 3.3V

- Programmable impedance

- Hot-socketing

- Flexible bus-maintenance (Pull-up, pulldown, bus-keeper, or none)

- Open drain operation

- SSTL 2, 3 (I & II)

- HSTL (I, III, IV)

- PCI-X, PCI 3.3

- GTL+

- LVDS

- LVPECL

#### ■ Expanded In-System Programmability (ispXP<sup>™</sup>)

**Advance Data Sheet**

- Instant-on capability

- Single chip convenience

- In-System Programmable via IEEE 1532

Interface

- Infinitely reconfigurable via IEEE 1532 or sysCONFIG<sup>™</sup> microprocessor interface

- Design security

#### ■ High Speed Operation

- 3.5ns pin-to-pin delays, 285MHz f<sub>MAX</sub>

- Deterministic timing

- Low Power Consumption

- Static power 20 to 50mA (1.8V) 30 to 60mA (2.5/3.3V)

- 1.8V core for low dynamic power

- Easy System Integration

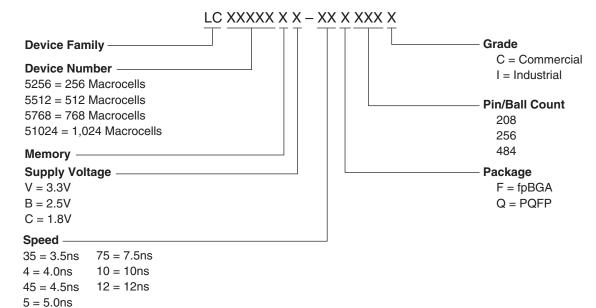

- 3.3V (5000MV), 2.5V (5000MB) and 1.8V (5000MC) power supply operation

- · IEEE 1149.1 interface for boundary scan testing

- sysIO quick configuration

- Density migration

- Multiple density and package options

- PQFP and fine pitch BGA packaging

#### Table 1. ispXPLD 5000MX Family Selection Guide

|                                                | ispXPLD 5256MX | ispXPLD 5512MX                     | ispXPLD 5768MX         | ispXPLD 51024MX        |

|------------------------------------------------|----------------|------------------------------------|------------------------|------------------------|

| Macrocells                                     | 256            | 512                                | 768                    | 1,024                  |

| Multi-Function Blocks                          | 8              | 16                                 | 24                     | 32                     |

| Maximum RAM Bits                               | 128K           | 256K                               | 384K                   | 512K                   |

| Maximum CAM Bits                               | 48K            | 96K                                | 144K                   | 192K                   |

| sysCLOCK PLLs                                  | 2              | 2                                  | 2                      | 2                      |

| t <sub>PD</sub> (Propagation Delay)            | 3.5ns          | 4.0ns                              | 4.5ns                  | 4.5ns                  |

| t <sub>S</sub> (Register Set-up Time)          | 2.5ns          | 2.9ns                              | 3.0ns                  | 3.0ns                  |

| t <sub>CO</sub> (Register Clock to Out Time)   | 2.5ns          | 3.0ns                              | 3.0ns                  | 3.0ns                  |

| f <sub>MAX</sub> (Maximum Operating Frequency) | 285MHz         | 250MHz                             | 225MHz                 | 225MHz                 |

| I/Os                                           | 141            | 149/193/253                        | 193/317                | 317/381                |

| System Gates                                   | 75K            | 150K                               | 225K                   | 300K                   |

| Packages                                       | 256 fpBGA      | 208 PQFP<br>256 fpBGA<br>484 fpBGA | 256 fpBGA<br>484 fpBGA | 484 fpBGA<br>672 fpBGA |

# Introduction

The ispXPLD 5000MX family represents a new class of device, referred to as the eXpanded Programmable Logic Devices (XPLDs). These devices extend the capability of Lattice's popular SuperWIDE ispMACH 5000 architecture by providing flexible memory capability. The family supports single- or dual-port SRAM, FIFO, and ternary CAM operation. In addition, sysCLOCK PLLs and sysIO interfaces provide support for the system-level needs of designers.

The devices provide designers with a convenient one-chip solution that provides logic availability at boot-up, design security, and extreme reconfigurability. The use of advanced process technology provides industry-leading performance with combinatorial propagation delay as low as 3.5ns, 2.5ns clock-to-out delay, 2.0ns set-up time, and operating frequency up to 285MHz. This performance is coupled with low static and dynamic power consumption. The ispXPLD 5000MX architecture provides predictable deterministic timing.

The availability of 3.3, 2.5 and 1.8V versions of these devices along with the flexibility of the sysIO interface helps users meet the challenge of today's mixed voltage designs. Boundary scan testability further eases integration into today's complex systems. A variety of density and package options increase the likelihood of a good fit for a particular application. Table 1 shows the members of the ispXPLD 5000MX family.

# Architecture

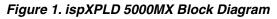

The ispXPLD 5000MX devices consist of Multi-Function Blocks (MFBs) interconnected with a Global Routing Pool. Signals enter and leave the device via one of four sysIO banks. Figure 1 shows the block diagram of the ispXPLD 5000MX. Incoming signals may connect to the global routing pool or the registers in the MFBs. An Output Sharing

#### Lattice Semiconductor

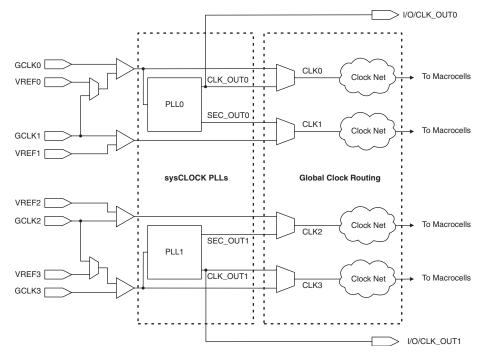

Array (OSA) increases the number of I/O available to each MFB, allowing a complete function high-performance access to the I/O. There are four clock pins that drive four global clock nets within the device. Two sysCLOCK PLLs are provided to allow the synthesis of new clocks and control of clock skews.

### **Multi-Function Block (MFB)**

Each MFB in the ispXPLD 5000MX architecture can be configured in one of the six following modes. This provides a flexible approach to implementing logic and memory that allows the designer to achieve the mix of functions that are required for a particular design, maximizing resource utilization. The six modes supported by the MFB are:

- SuperWIDE Logic Mode

- True Dual-port SRAM Mode

- Pseudo Dual-port SRAM Mode

- Single-port SRAM Mode

- FIFO Mode

- Ternary CAM Mode

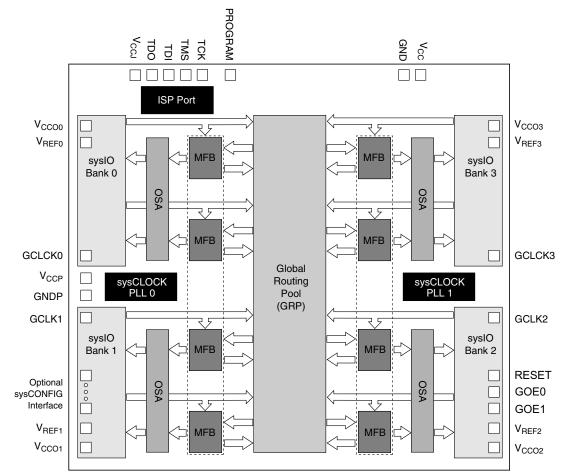

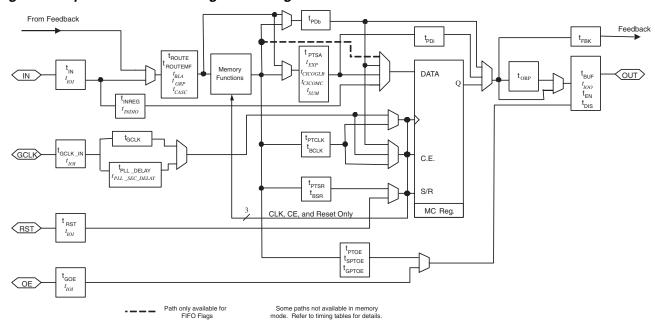

The MFB consists of a multi-function array and associated routing. Depending on the chosen functions the multifunction array uses up to 68 inputs from the GRP and the four global clock and reset signals. The array outputs data along with certain control functions to the macrocells. Output signals can be routed internally for use elsewhere in the device and to the sysIO banks for output. Figure 2 shows the block diagram of the MFB. The various configurations are described in more detail in the following sections.

#### Figure 2. MFB Block Diagram

3

#### **Cascading For Wide Operation**

In several modes it is possible to cascade adjacent MFBs to support wider operation. Table 2 details the different cascading options. There are chains of MFBs in each device which determine those MFBs that are adjacent for the purposes of cascading. Table 3 indicates these chains. The ispXPLD 5000MX design tools automatically cascade blocks if required by a particular design.

Table 2. Cascading Modes For Wide Support

| Mode  | Cascading Function                                                                       |  |  |

|-------|------------------------------------------------------------------------------------------|--|--|

| Logic | Input Width. Allows two MFBs to act as a 136-input block.                                |  |  |

| LUGIC | Arithmetic. Allow the carry chain to pass between two MFBs.                              |  |  |

| FIFO  | Memory Width Expansion. Allows MFBs to be cascaded for greater width support.            |  |  |

| CAM   | Memory Width Expansion. Allows up to four MFBs to be cascaded for greater width support. |  |  |

Table 3. MFB Cascade Chain

| Device           | MFBs in Cascade Chain                                                                                                                                                                                                 |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ispXPLD 5256MX   | $A \to B \to C \to D$                                                                                                                                                                                                 |  |  |

| ISPAPED 5250IVIA | $E \to F \to G \to H$                                                                                                                                                                                                 |  |  |

| ispXPLD 5512MX   | $A \to B \to C \to D \to E \to F \to G \to H$                                                                                                                                                                         |  |  |

|                  | $P \to O \to N \to M \to L \to K \to J \to I$                                                                                                                                                                         |  |  |

| ispXPLD 5768MX   | $D \to C \to B \to A \to X \to W \to V \to U \to T \to S \to R \to Q$                                                                                                                                                 |  |  |

|                  | $E \to F \to G \to H \to I \to J \to K \to L \to M \to N \to O \to P$                                                                                                                                                 |  |  |

| ispXPLD 51024MX  | $H \to G \to F \to E \to D \to C \to B \to A \to AF \to AE \to AD \to AC \to AB \to AA \to Z \to Y$                                                                                                                   |  |  |

|                  | $I \rightarrow J \rightarrow K \rightarrow L \rightarrow M \rightarrow N \rightarrow O \rightarrow P \rightarrow Q \rightarrow R \rightarrow S \rightarrow T \rightarrow U \rightarrow V \rightarrow W \rightarrow X$ |  |  |

# SuperWIDE Logic Mode

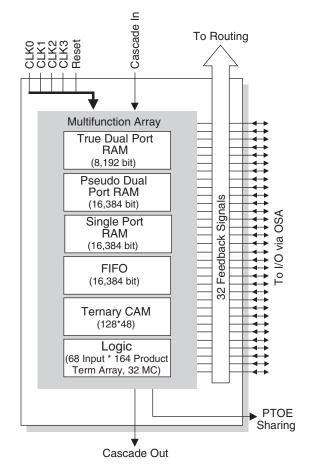

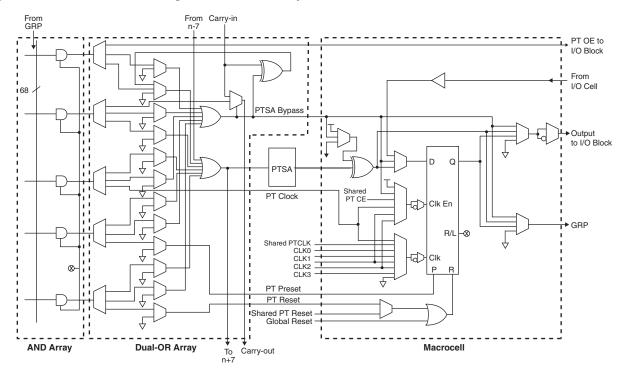

In logic mode, each MFB contains 32 macrocells and a fully populated, programmable AND-array with 160 logic product terms and four control product terms. The MFB has 68 inputs from the Global Routing Pool, which are available in both true and complement form for every product term. It is also possible to cascade adjacent MFBs to create a block with 136 inputs. The four control product terms are used for shared reset, clock, clock enable, and output enable functions. Figure 3 shows the overall structure of the MFB in logic mode while Figure 4 provides a more detailed view from the perspective of a macrocell slice.

#### Figure 3. MFB in SuperWIDE Logic Mode

Figure 4. Macrocell Slice in Logic Mode AND-Array

#### **AND-Array**

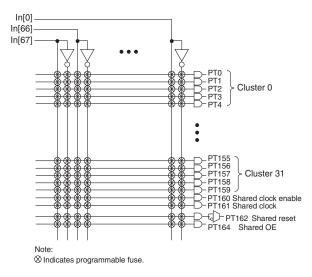

The programmable AND-Array consists of 68 inputs and 164 output product terms. The 68 inputs from the GRP are used to form 136 lines in the AND-Array (true and complement of the inputs). Each line in the array can be connected to any of the 164 output product terms via a wired AND. Each of the 160 logic product terms feed the Dual-OR Array with the remaining four control product terms feeding the Shared PT Clock, Shared PT Clock Enable, Shared PT Reset and Shared PT OE. Starting with PTO sets of five product terms form product terms, the first, third, fourth and fifth product terms of each cluster can be used as a PTOE, PT Clock, PT Preset and PT Reset, respectively. Figure 5 is a graphical representation of the AND-Array.

#### Figure 5. AND Array

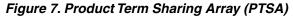

### **Dual-OR Array (Including Arithmetic Support)**

The Dual-OR Array consists of 64 OR gates. There are two OR gates per macrocell in the MFB. These OR gates are referred to as the Expandable PTSA OR gate and the PTSA-Bypass OR gate. The PTSA-Bypass OR gate receives its five inputs from the combination of product terms associated with the product term cluster. The PTSA-Bypass OR gate feeds the macrocell directly for fast narrow logic. The Expandable PTSA OR gate receives five inputs from the combination of product terms associated with the product term cluster. It also receives an additional input from the Expanded PTSA OR gate of the N-7 macrocell, where N is the number of the macrocell associated with the current OR gate. The Expandable PTSA OR gate feeds the PTSA for sharing with other product terms and the N+7 Expandable PTSA OR gate. This allows cascading of multiple OR gates for wide functions. There is a small timing adder for each level of expansion. Figure 6 is a graphical representation of the Dual-OR Array.

The Dual-OR PT sharing array also contains logic to aid in the efficient implementation of arithmetic functions. This logic takes Carry In and allows the generation of Carry Out along with a SUM signal. Subtractors can be implemented using the two's complement method. Carry is propagated from macrocells 0 to macrocell 31. Macrocell zero can have its carry input connected to the carry output of macrocell 31 in an adjacent MFB or it can be set to zero or one. If a macrocell is not used in an arithmetic function carry can bypass it. The carry chain flows is the same as that for PT cascading.

#### Figure 6. Dual-OR PT Sharing Array

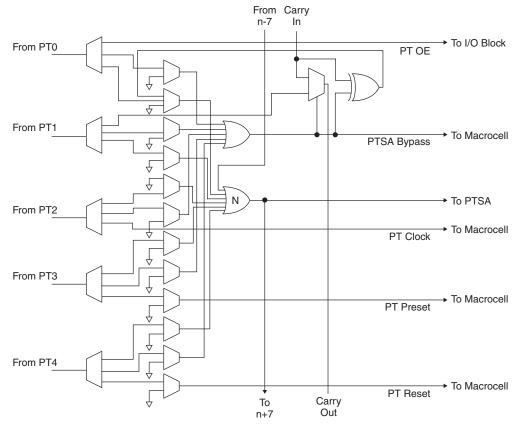

#### **Product Term Sharing Array**

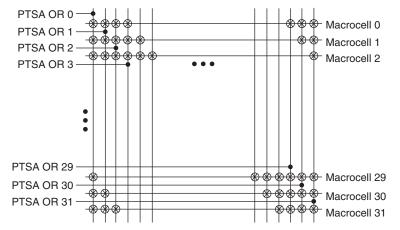

The Product Term Sharing Array (PTSA) consists of 32 inputs from the Dual-OR Array (Expandable PTSA OR) and 32 outputs directly to the macrocells. Each output is the OR term of any combination of the seven Expandable PTSA OR terms connected to that output. Every Nth macrocell is connected to N-3, N-2, N-1, N, N+1, N+2 and N+3 PTSA OR terms via a programmable connection. This wraps around the logic, for example, Macrocell 0 gets its logic from 29, 30, 31, 0, 1, 2, 3. The Expandable PTSA OR used in conjunction with the PTSA allows wide functions to be implemented easily and efficiently. Without using the Expandable PTSA OR capability, the greatest number of product terms that can be included in a single function with one pass of delay is 35. Up to 160 product terms can be included in a single function through the use of the expandable PTSA OR capability. Figure 7 shows the graphical representation of the PTSA.

#### Lattice Semiconductor

#### Macrocell

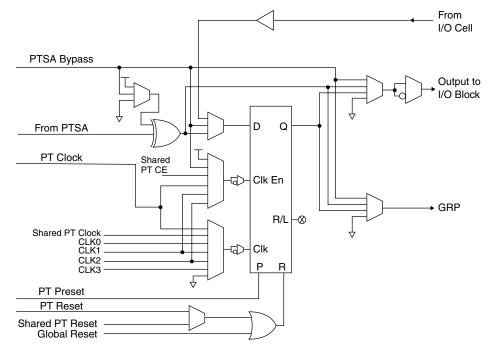

The 32 registered macrocells in the MFB are driven by the 32 outputs from the PTSA or the PTSA bypass. Each macrocell contains a programmable XOR gate, a programmable register/latch flip-flop and the necessary clocks and control logic to allow combinatorial or registered operation. All macrocells have an output that feeds the GRP. Selected macrocells have an additional output that feeds the OSA and hence I/Os. This dual or concurrent output capability from the macrocell gives efficient use of the hardware resources. One output can be a registered function for example, while the other output can be an unrelated combinatorial function. A direct register input from the I/O cell facilitates efficient use of the macrocell to construct high-speed input registers. Macrocell registers can be clocked from one of several global or product term clocks available on the device. A global and product term clock enable is also provided, eliminating the need to gate the clock to the macrocell registers directly. Reset and preset for the macrocell register is provided from both global and product term signals. The macrocell register can be programmed to operate as a D-type register or a D-type latch. Figure 8 is a graphical representation of the macrocell.

#### Figure 8. Macrocell

### **Memory Modes**

The ispXPLD 5000MX architecture allows the MFB to be configured as a variety of memory blocks as detailed in Table 4. The remainder of this section details operation of each of the memory modes. Additional information regarding the memory modes can also be found in technical note number TN1030, *Using Memory in ispXPLD 5000MX Devices*.

#### Table 4. MFB Memory Configuration

| Memory Mode                         | Configurations |

|-------------------------------------|----------------|

| Dual-port                           | 8,192 x 1      |

|                                     | 4,096 x 2      |

|                                     | 2,048 x 4      |

|                                     | 1,024 x 8      |

|                                     | 512 x 16       |

| Single-port, Pseudo Dual Port, FIFO | 16,384 x1      |

|                                     | 8,192 x 2      |

|                                     | 4,096 x 4      |

|                                     | 2048 x 8       |

|                                     | 1024 x 16      |

|                                     | 512 x 32       |

| САМ                                 | 128 x 48       |

#### Input and Output

The data input and control signals to a MFB in memory mode are generated from inputs from the routing. Data signals are only available in the true non-inverted format. True or complemented versions of the inputs are available for generating the control signals. Data and flag outputs are fed from the MFB to the GRP and OSA. Unused inputs and outputs are not accessible in memory mode.

#### **ROM Operation**

In each of the memory modes it is possible to specify the power-on state of each bit in the memory array. This allows the memory to be used as ROM if desired.

#### **Increased Depth And Width**

Designs that require a memory depth or width that is greater than that support by a single MFB can be supported by cascading multiple blocks. For dual port, single port, and pseudo dual port modes additional width is easily provided by sharing address lines. Additional depth is supported by multiplexing the RAM output. For FIFO and CAM modes additional width is supported through the cascading of MFBs.

The Lattice design tools automatically combine blocks to support the memory size specified in the user's design.

#### **Bus Size Matching**

All of the memory modes apart from CAM mode support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1 and so on. Although the word size and number of words for each port varies this mapping scheme applies to each port.

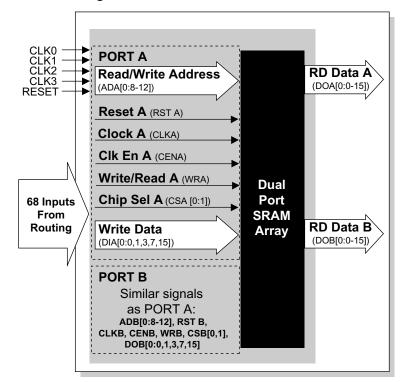

#### True Dual-Port SRAM Mode

In Dual-Port SRAM Mode the multi-function array is configured as a dual port SRAM. In this mode two independent read/write ports access the same 8,192-bits of memory. Data widths of 1, 2, 4, 8, and 16 are supported by the MFB. Figure 9 shows the block diagram of the dual port SRAM.

Write data, address, chip select and read/write signals are always synchronous (registered.) The output data signals can be synchronous or asynchronous. Resets are asynchronous. All inputs on the same port share the same clock, clock enable, and reset selections. All outputs on the same port share the same clock, clock enable, and reset selections. Selections may be made independently between both inputs and outputs and ports. Table 5 shows the possible sources for the clock, clock enable and initialization signals for the various registers.

Figure 9. Dual-Port SRAM Block Diagram

Table 5. Register Clock, Clock Enable, and Reset in Dual-Port SRAM Mode

| Register                                                                       | Input        | Source                                                                                                                    |

|--------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------|

| Address, Write Data,<br>Read Data, Read/<br>Write, and Chip<br>Select<br>Reset | Clock        | Selected from CLKA (CLKB) or one of the global clocks (CLK0 - CLK3).<br>The selected signal can be inverted if desired.   |

|                                                                                | Clock Enable | Selected from CENA (CENB) or two of the global clocks (CLK1 - CLK 2).<br>The selected signal can be inverted if required. |

|                                                                                | Reset        | Created by the logical OR of the global reset signal and RSTA (RSTB).<br>RSTA (RSTB) can be inverted is desired.          |

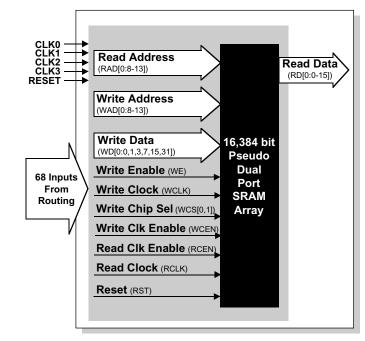

#### Pseudo Dual-Port SRAM Mode

In Pseudo Dual-Port SRAM Mode the multi-function array is configured as a SRAM with an independent read and write ports that access the same 16,384-bits of memory. Data widths of 1, 2, 4, 8, 16 and 32 are supported by the MFB. Figure 10 shows the block diagram of the Pseudo Dual-Port SRAM.

Write data, write address, chip select and write enable signals are always synchronous (registered). The read data and read address signals can be synchronous or asynchronous. Reset is asynchronous. All write signals share the same clock, and clock enable. All read signals share the same clock and clock enable. Reset is shared by both read and write signals. Table 6 shows the possible sources for the clock, clock enable and initialization signals for the various registers.

Figure 10. Pseudo Dual-Port SRAM Block Diagram

Table 6. Register Clock, Clock Enable, and Reset in Pseudo Dual-Port SRAM Mode

| Register                                                             | Input        | Source                                                                                                           |

|----------------------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------|

| Write Address, Write<br>Data, Write Enable,<br>and Write Chip Select | Clock        | Selected from WCLK or one of the global clocks (CLK0 - 3).<br>The selected signal can be inverted if desired.    |

|                                                                      | Clock Enable | Selected from WCEN or two of the global clocks (CLK0 - CLK3).<br>The selected signal can be inverted if desired. |

|                                                                      | Reset        | Created by the logical OR of the global reset signal and RST.<br>RST may have inversion if desired.              |

|                                                                      | Clock        | Selected from RCLK or one of the global clocks (CLK0 - 3).<br>The selected signal can be inverted if desired.    |

| Read Data and Read<br>Address                                        | Clock Enable | Selected from RCEN or two of the global clocks (CLK1 - CLK2).<br>The selected signal can be inverted if desired. |

|                                                                      | Reset        | Created by the logical OR of the global reset signal and RST.<br>RST may have inversion if desired.              |

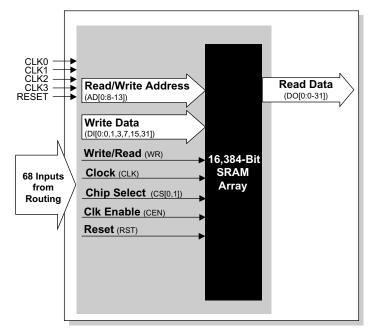

#### Single-Port SRAM Mode

In Single-Port SRAM Mode the multi-function array is configured as a single-port SRAM. In this mode one ports accesses 16,384-bits of memory. Data widths of 1, 2, 4, 8, 16 and 32 are supported by the MFB. Figure 11 shows the block diagram of the single-port SRAM.

Write data, address, chip select and read/write signals are always synchronous (registered.) The output data signals can be synchronous or asynchronous. Reset is asynchronous. All signals share a common clock, clock enable, and reset. Table 7 shows the possible sources for the clock, clock enable and reset signals.

Figure 11. Single-Port SRAM Block Diagram

Table 7. Register Clock, Clock Enable, and Reset in Single-Port SRAM Mode

| Register             | Input | Source                                                                                                                                      |  |

|----------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| Address, Write Data, |       | CLK or one of the global clocks (CLK0 - CLK3). Each of these signals can be inverted if required.                                           |  |

|                      |       | CEN or two of the global clocks (CLK1 - CLK 2). Each of these signals can be inverted if required.                                          |  |

|                      |       | Created by the logical OR of the global reset signal and RST. RST is routed by the multifunction array from GRP, with inversion if desired. |  |

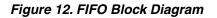

#### **FIFO Mode**

In FIFO Mode the multi-function array is configured as a FIFO (First In First Out) buffer with built in control. The read and write clocks can be different or the same dependent on the application. Four flags show the status of the FIFO; Full, Empty, Almost Full, and Almost empty. The thresholds for Full, Almost full and Almost empty are programmable by the user. It is possible to reset the read pointer, allowing support of frame retransmit in communications applications. If desired, the block can be used in show ahead mode allowing the early reading of the next read address.

In this mode one ports accesses 16,384-bits of memory. Data widths of 1, 2, 4, 8, 16 and 32 are supported by the MFB. Figure 12 shows the block diagram of the FIFO.

Write data, write enable, flag outputs and read enable are synchronous. The Write Data, Almost Full and Full share the same clock and clock enables. Read outputs are synchronous although these can be configured in look ahead mode. The Read Data, Empty and Almost Empty signals share the same clock and clock enables. Reset is shared by all signals. Table 8 shows the possible sources for the clock, clock enable and reset signals for the various registers.

| Register                           | Input | Source                                                                                                                                     |

|------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Write Enchle                       |       | WCLK or one of the global clocks (CLK0 - CLK3). Each of these signals can be inverted if required.                                         |

|                                    |       | WEN or two of the global clocks (CLK1 - CLK 2). Each of these signals can be inverted if required.                                         |

|                                    | Reset | N/A                                                                                                                                        |

| Full and                           | Clock | WCLK or one of the global clocks (CLK0 - CLK3). Each of these signals can be inverted if required.                                         |

| Almost Full Clock<br>Flags Enable  |       | WEN or two of the global clocks (CLK1 - CLK 2). Each of these signals can be inverted if required.                                         |

|                                    | Reset | Created by the logical OR of the global reset signal and RST. RST is routed by the multifunction array from GRP, with inversion if desired |

|                                    | Clock | RCLK or one of the global clocks (CLK0 - CLK3). Each of these signals can be inverted if required.                                         |

| Empty and<br>Almost Empty<br>Flags |       | REN or two of the global clocks (CLK1 - CLK 2). Each of these signals can be inverted if required.                                         |

|                                    | Reset | Created by the logical OR of the global reset signal and RST. RST is routed by the multifunction array from GRP, with inversion if desired |

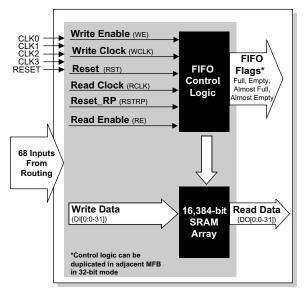

#### CAM Mode

In CAM Mode the multi-function array is configured as a Ternary Content Addressable Memory (CAM). CAM behaves like a reverse memory where the input is data and the output is an address. It can be used to perform a variety of high-performance look-up functions. As such, CAM has two modes of operation. In write or update mode the CAM behaves as a RAM and data is written to the supplied address. In read or compare operations data is supplied to the CAM and if this matches any of the data in the array the Match and Multiple Match (if there is more than one match) flags are set to true and the lowest address with matching data is output. The CAM contains 128 entries of 48 bits. Figure 13 shows the block diagram of the CAM.

To further enhance the flexibility of the CAM a mask register is available. If enabled during updates, bits corresponding with those set to 1 in the mask register are not updated. If enabled during compare operations, bits corresponding to those set to 1 in the mask register are not included in the compare. A write don't care signal allows don't cares to be programmed into the CAM if desired. Like other write operations the mask register controls this.

The write/comp data, write address, write enable, write chip select, and write don't care signals are synchronous. The CAM Output signals, match flag, and multimatch flag can be synchronous or asynchronous. The Enable mask register input is not latched but must meet setup and hold times relative to the write clock. All inputs must use the same clock and clock enable signals. All outputs must use the same clock and clock enable signals. Reset is common for both inputs and outputs. Table 9 shows the allowable sources for clock, clock enable, and reset for the various CAM registers.

#### Figure 13. CAM Mode

#### Table 9. Register Clocks, Clock Enables, and Initialization in CAM Mode

| Register                                                                                                                                              | Input        | Source                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Write data, Write address,<br>Enable mask register, Write<br>enable, write chip select, and<br>write don't care, CAM Output,<br>Match, and Multimatch |              | CLK or one of the global clocks (CLK0 - CLK3). Each of these signals can be inverted if required.                                          |

|                                                                                                                                                       | Clock Enable | WE or two of the global clocks (CLK1 - CLK 2). Each of these signals can be inverted if required.                                          |

|                                                                                                                                                       | Reset        | Created by the logical OR of the global reset signal and RST. RST is routed by the multifunction array from GRP, with inversion if desired |

### **Clock Distribution**

The ispXPLD 5000MX family has four dedicated clock input pins: GCLK0-GCLK3. GLCK0 and GCLK3 can be routed through a PLL circuit or routed directly to the internal clock nets. The internal clock nets (CLK0-CLK3) are directly related to the dedicated clock pins (see Secondary Clock Divider exception when using the sysCLOCK circuit). These feed the registers in the MFBs. Note at each register there is the option of inverting the clock if required. Figure 14 shows the clock distribution network.

#### Figure 14. Clock Distribution Network

# sysCLOCK PLL

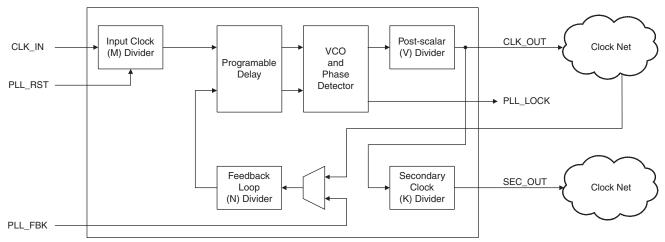

The sysCLOCK PLL circuitry consists of Phase-Lock Loops (PLLs) and the various dividers, reset and feedback signals associated with the PLLs. This feature gives the user the ability to synthesize clock frequencies and generate multiple clock signals for routing within the device. Furthermore, it can generate clock signals that are deskewed either at the board level or the device level.

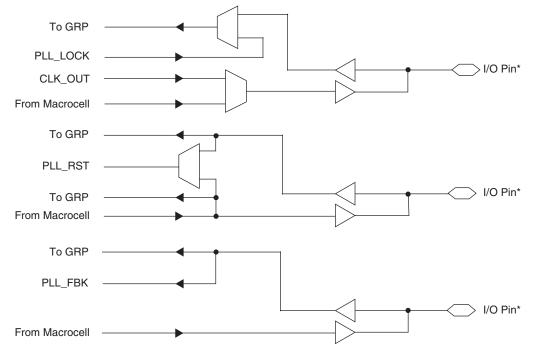

The ispXPLD 5000MX devices provide two PLL circuits. PLL0 receives its clock inputs from GCLK 0 and provides outputs to CLK 0 (CLK 1 when using the secondary clock). PLL1 operates with signals from GCLK 3 and CLK 3 (CLK 2 when using the secondary clock). The optional outputs CLK\_OUT can be routed to an I/O pin. The optional PLL\_LOCK output is routed into the GRP. The optional input PLL\_RST can be routed either from the GRP or directly from an I/O pin. The optional PLL\_FBK into can be routed directly from a pin. Figure 15 shows the ispXPLD 5000MX PLL block diagram. Figure 16 shows the connection of optional inputs and outputs.

#### Lattice Semiconductor

#### Figure 15. PLL Block Diagram

Figure 16. Connection of Optional PLL Inputs and Outputs

\*See pinout table for details

In order to facilitate the multiply and divide capabilities of the PLL, each PLL has dividers associated with it: M, N and K. The M divider is used to divide the clock signal, while the N divider is used to multiply the clock signal. The K divider is only used when a secondary clock output is needed. This divider divides the primary clock output and feeds to a separate global clock net. The V divider is used to provide lower frequency output clocks, while maintaining a stable, high frequency output from the PLL's VCO circuit. The PLL also has a delay feature that allows the output clock to be advanced or delayed to improve set-up and clock-to-out times for better performance. For more information on the PLL, please refer to Lattice technical note number TN1003, *Lattice sysCLOCK PLL Usage Guidelines*.

### sysIO Banks

The ispXPLD 5000MX devices are divided into four sysIO banks, consisting of multiple I/O cells, where each bank is capable of supporting 16 different I/O standards. Each sysIO bank has its own I/O voltage ( $V_{CCO}$ ) and reference voltage ( $V_{BFF}$ ) resources allowing complete independence from the others.

### I/O Cell

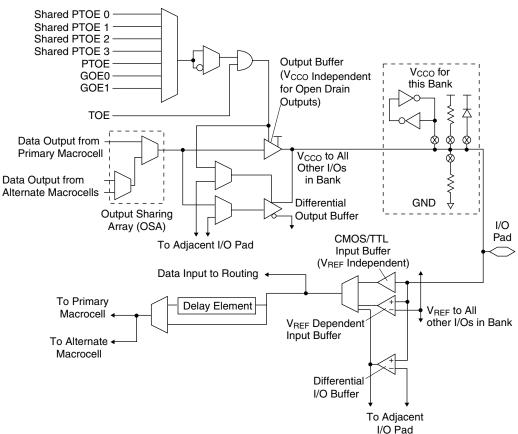

The I/O cell of the ispXPLD 5000MX devices contains an output enable (OE) MUX, a programmable tri-state output buffer, a programmable input buffer, and programmable bus-maintenance circuitry.

The I/O cell receives inputs from its associated macrocells and the device pin. The I/O cell has a feedback line to its associated macrocells and a direct path to GRP. The output enable (OE) MUX selects the OE signal per I/O cell. The inputs to the OE MUX are the four global PTOE signals, PTOE and the two GOE signals. The OE MUX also has the ability to choose either the true or inverse of each of these signals. The output of the OE MUX goes through a logical AND with the TOE signal to allow easy tri-stating of the outputs for testing purposes. The MFBs are grouped into segments of four for the purpose of generating Shared PTOE signals. Each Shared PTOE signal is derived from PT 163 from one of the four MFBs. Table 10 shows the segments. The PTOE signal is derived from the first product term in each macrocell cluster, which is directly routed to the OE MUX. Therefore, every I/O cell can have a different OE signal. Figure 17 is a graphical representation of the I/O cell.

#### Figure 17. I/O Cell

#### Table 10. Shared PTOE Segments

| Device          | MFBs Associated With Segments                                                                                          |

|-----------------|------------------------------------------------------------------------------------------------------------------------|

| ispXPLD 5256MX  | (A, B, C, D) (E, F, G, H)                                                                                              |

| ispXPLD 5512MX  | (A, B, C, D) (E, F, G, H)<br>(I, J, K, L) (M, N, O, P)                                                                 |

| ispXPLD 5768MX  | (A, B, C, D) (E, F, G, H)<br>(I, J, K, L) (M, N, O, P)<br>(Q, R, S, T) )U, V, W, Z)                                    |

| ispXPLD 51024MX | (A, B, C, D) (E, F, G, H)<br>(I, J, K, L) (M, N, O, P)<br>(Q, R, S, T) (U, V, W, Z)<br>(Y, Z, AA, AB) (AC, AD, AE, AF) |

#### sysIO Standards

Each I/O within a bank is individually configurable based on the V<sub>CCO</sub> and V<sub>REF</sub> settings. Some standards also require the use of an external termination voltage. Table 11 lists the sysIO standards with the typical values for V<sub>CCO</sub>, V<sub>REF</sub> and V<sub>TT</sub>. For more information on the sysIO capability, please refer to Lattice technical note number TN1000, *sysIO Design and Usage Guidelines*.

| sysIO Standard       | Nominal V <sub>CCO</sub> | Nominal V <sub>REF</sub> | Nominal V <sub>TT</sub> |

|----------------------|--------------------------|--------------------------|-------------------------|

| LVTTL                | 3.3V                     | N/A                      | N/A                     |

| LVCMOS-3.3           | 3.3V                     | N/A                      | N/A                     |

| LVCMOS-2.5           | 2.5V                     | N/A                      | N/A                     |

| LVCMOS-1.8           | 1.8V                     | N/A                      | N/A                     |

| PCI 3.3V             | N/A                      | N/A                      | N/A                     |

| PCI-X 3.3V           | N/A                      | N/A                      | N/A                     |

| AGP-1X               | 3.3V                     | N/A                      | N/A                     |

| SSTL3, Class I & II  | 3.3V                     | 1.5V                     | 1.5V                    |

| SSTL2, Class I & II  | 2.5V                     | 1.25V                    | 1.25V                   |

| CTT 3.3              | 3.3V                     | 1.5V                     | 1.5V                    |

| CTT 2.5              | 2.5V                     | 1.25V                    | 1.25V                   |

| HSTL, Class I        | 1.5V                     | 0.75V                    | 0.75V                   |

| HSTL, Class III      | 1.5V                     | 0.9V                     | 0.75v                   |

| HSTL, Class IV       | 1.5V                     | 0.9V                     | 0.75v                   |

| GTL+                 | N/A                      | 1.0V                     | 1.5V                    |

| LVPECL, Differential | 2.5V, 3.3V               | N/A                      | N/A                     |

| LVDS                 | 2.5V, 3.3V               | N/A                      | N/A                     |

Table 11. ispXPLD 5000MX Supported I/O Standards

#### Control, Clock, and JTAG Signals

Global clock pins support the same sysIO standards as general purpose I/O. When required the  $V_{\text{REF}}$  signal is derived from the adjacent bank. When differential standards are supported two adjacent clock pins are paired to form the input. The TOE and JTAG pins of the ispXPLD 5000MX device are the only pins that do not have sysIO capabilities. These pins only support the LVTTL and LVCMOS standards applicable to the power supply voltage of the device. The global reset global output enable pins are associated with Bank 2 and support all of the sysIO standards.

#### Hotsocketing

The I/O on the ispXPLD 5000MX devices are well suited for those applications that require hot socketing capability, when configured as LVCMOS or LVTTL. Hot socketing a device requires that the device, when powered down, can

tolerate active signals on the I/Os and inputs without being damaged. Additionally, it requires that the effects of the powered-down device be minimal on active signals.

#### Programmable Drive Strength

The drive strength of I/Os that are programmed as LVCMOS is tightly controlled and can be programmed to a variety of different values. Thus the impedance an output driver can be closely match to the characteristic impedance of the line it is driving. This allows users to eliminate the need for external series termination resistors.

#### Programmable Slew Rate

The slew rate of outputs is carefully controlled. When outputs are configured as LVCMOS the devices support two slew rates. This allows system noise and performance to be balanced in a design.

#### **Programmable Bus-Maintenance**

All general-purpose inputs have programmable bus maintenance circuitry. These are intended to maintain a valid logic level into a device when driving devices go into the tri-state mode. Four options are available for users; pull-up, pull-down, bus-keeper, or nothing.

### Expanded In-System Programmability (ispXP)

The ispXPLD 5000MX family utilizes a combination of EEPROM non-volatile cells and SRAM technology to deliver a logic solution that provides "instant-on" at power-up, a convenient single chip solution, and the capability for infinite reconfiguration. A non-volatile array distributed within the device stores the device configuration. At power-up this information is transferred in a massively parallel fashion into SRAM bits that control the operation of the device.

#### **IEEE 1532 ISP**

In-system programming of devices provides a number of significant benefits including rapid prototyping, lower inventory levels, higher quality and the ability to make in-field modifications. All ispXPLD 5000MX devices provide in-system programmability through their Boundary Scan Test Access Port. This capability has been implemented in a manner that ensures that the port remains compliant to the IEEE 1532 standard. By using IEEE 1532 as the communication interface through which ISP is achieved, customers get the benefit of a standard, well-defined interface.

The IEEE1532 programming interface allows programming of either the non-volatile array or reconfiguration of the SRAM bits.

The ispXPLD 5000MX devices can be programmed across the commercial temperature and voltage range. The PC-based Lattice software facilitates in-system programming of ispXPLD 5000MX devices. The software takes the JEDEC file output produced by the design implementation software, along with information about the scan chain, and creates a set of vectors used to drive the scan chain. The software can use these vectors to drive a scan chain via the parallel port of a PC. Alternatively, the software can output files in formats understood by common automated test equipment. This equipment can then be used to program ispXPLD 5000MX devices during the testing of a circuit board.

#### sysCONFIG Interface

In addition to being able to program the device through the IEEE 1532 interface a microprocessor style interface (sysCONFIG interface) allows reconfiguration of the SRAM bits within the device. For more information on the sysCONFIG capability, please refer to technical note number TN1026, *sysCONFIG Interface Usage Guidelines*.

#### Security Scheme

A programmable security scheme is provided on the ispXPLD 5000MX devices as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, this bit prevents readback of the programmed pattern by a device programmer, securing proprietary designs from competitors. The security bit also prevents programming and verification. The entire device must be erased in order to erase the security bit.

### Low Power Consumption

The ispXPLD 5000MX devices use zero power non-volatile cells along with full CMOS design to provide low static power consumption. The 1.8V core reduces dynamic power consumption compared with devices with higher core voltages. For information on estimating power consumption, please refer to Lattice technical note number TN1031, *Power Estimation in ispXPLD 5000MX Devices.*

### **Density Migration**

The ispXPLD 5000MX family has been designed to ensure that different density devices in the same package have compatible pin-outs. Furthermore, the architecture ensures a high success rate when performing design migration from lower density parts to higher density parts. In many cases, it is possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case.

# IEEE 1149.1-Compliant Boundary Scan Testability

All ispXPLD 5000MX devices have boundary scan cells and are compliant to the IEEE 1149.1 standard. This allows functional testing of the circuit board on which the device is mounted through a serial scan path that can access all critical logic notes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test node data to be captured and shifted out for verification. In addition, these devices can be linked into a board-level serial scan path for board-level testing. The test access port has its own supply voltage and can operate with LVCMOS3.3, 2.5 and 1.8V standards.

#### sysIO Quick Configuration

To facilitate the most efficient board test, the physical nature of the I/O cells must be set before running any continuity tests. As these tests are fast, by nature, the overhead and time that is required for configuration of the I/Os' physical nature should be minimal so that board test time is minimized. The ispXPLD 5000MX family of devices allows this by offering the user the ability to quickly configure the physical nature of the sysIO cells. This quick configuration takes milliseconds to complete, whereas it takes seconds for the entire device to be programmed. Lattice's ispVM<sup>™</sup> System programming software can either perform the quick configuration through the PC parallel port, or can generate the ATE or test vectors necessary for a third-party test system.

# Absolute Maximum Ratings<sup>1, 2, 3</sup>

|                                                           | ispXPLD 5000MC<br>1.8V | ispXPLD 5000MB/V<br>2.5V/3.3V |

|-----------------------------------------------------------|------------------------|-------------------------------|

| Supply Voltage (V <sub>CC</sub> )                         | 0.5 to 2.5V            | 0.5 to 5.5V                   |

| PLL Supply Voltage (V <sub>CCP</sub> )                    | 0.5 to 2.5V            | 0.5 to 5.5V                   |

| Output Supply Voltage (V <sub>CCO</sub> )                 | 0.5 to 4.5V            | 0.5 to 4.5V                   |

| IEEE 1149.1 TAP Supply Voltage (V <sub>CCJ</sub> )        | 0.5 to 4.5V            | 0.5 to 4.5V                   |

| Input Voltage Applied <sup>4</sup>                        | 0.5 to 4.5V            | 0.5 to 4.5V                   |

| Storage Temperature                                       | 65 to 150°C            | 65 to 150°C                   |

| Junction Temperature (T <sub>J</sub> ) with Power Applied | 55 to 150°C            |                               |

1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied (while programming, following the programming specifications).

2. Compliance with the Lattice *Thermal Management* document is required.

- 3. All voltages referenced to GND.

- 4. Overshoot and Undershoot of -2V to ( $V_{IHMAX}$  +2) volts is permitted for a duration of <20ns.

# **Recommended Operating Conditions**

| Symbol           | Parameter                                        | Min. | Max. | Units |

|------------------|--------------------------------------------------|------|------|-------|

|                  | Supply Voltage for 1.8V Devices (ispXPLD 5000MC) | 1.65 | 1.95 | V     |

| V <sub>CC</sub>  | Supply Voltage for 2.5V Devices (ispXPLD 5000MB) | 2.3  | 2.7  | V     |

|                  | Supply Voltage for 3.3V Devices (ispXPLD 5000MV) | 3    | 3.6  | V     |

|                  | PLL Block Supply Voltage for PLL 1.8V Devices    | 1.65 | 1.95 | V     |

| V <sub>CCP</sub> | PLL Block Supply Voltage for PLL 2.5V Devices    | 2.3  | 2.7  | V     |

|                  | PLL Block Supply Voltage for PLL 3.3V Devices    | 3    | 3.6  | V     |

| т                | Junction Temperature (Commercial Operation)      | 0    | 90   | С     |

| IJ               | Junction Temperature (Industrial Operation)      | -40  | 105  | С     |

### E<sup>2</sup>CMOS Erase Reprogram Specifications

| Parameter                          | Min   | Max | Units  |

|------------------------------------|-------|-----|--------|

| Erase/Reprogram Cycle <sup>1</sup> | 1,000 | —   | Cycles |

1. Valid over commercial temperature range.

# Hot Socketing Characteristics<sup>1, 2, 3, 4</sup>

| Symbol | Parameter                    | Condition                              | Min | Тур | Мах    | Units |

|--------|------------------------------|----------------------------------------|-----|-----|--------|-------|

| 1      | Input or I/O Leakage Current | $0 \le V_{IN} \le V_{IH}$ (MAX)        | —   | _   | +/-150 | μΑ    |

| DK     |                              | $V_{IH}$ (MAX) $\leq V_{IN} \leq 3.6V$ | —   | -   | +/-150 | μΑ    |

1. Insensitive to sequence of V<sub>CC</sub> and V<sub>CCO</sub>. However, assumes monotonic rise/fall rates for V<sub>CC</sub> and V<sub>CCO</sub>.

2.  $0 \le V_{CC} \le V_{CC}$  (MAX),  $0 \le V_{CCO} \le V_{CCO}$  (MAX)

3.  $I_{DK}$  is additive to  $I_{PU}$ ,  $I_{PD}$  or  $I_{BH}$ . Device defaults to pull-up until non-volatile cells are active.

4. LVTTL, LVCMOS only.

# **DC Electrical Characteristics**

| Symbol                                        | Parameter                                                                        | Condition                                        | Min.                    | Тур.          | Max.                    | Units  |

|-----------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------|-------------------------|---------------|-------------------------|--------|

| I <sub>IL,</sub> I <sub>IH</sub> <sup>1</sup> | Input or I/O Low leakage                                                         | $0 \le V_{IN} \le V_{IH} (MAX)$                  | —                       | —             | 10                      | uA     |

| I <sub>PU</sub>                               | I/O Active Pullup Current                                                        | $0 \le V_{IN} \le 0.7 V_{CCO}$                   | 30                      | —             | 150                     | uA     |

| I <sub>PD</sub>                               | I/O Active Pulldown Current                                                      | $V_{IL}$ (MAX) $\leq V_{IN} \leq V_{IH}$ (MAX)   | 30                      | —             | 150                     | uA     |

| I <sub>BHLS</sub>                             | Bus Hold Low Sustaining Current                                                  | $V_{IN} = V_{IL}$ (MAX)                          | 30                      | —             | -                       | uA     |

| I <sub>BHHS</sub>                             | Bus Hold High sustaining Current                                                 | $V_{IN} = 0.7 V_{CCO}$                           | 30                      | _             | —                       | uA     |

| I <sub>BHLO</sub>                             | Bus Hold Low Overdrive Current                                                   | $0 \le V_{IN} \le V_{IH} (MAX)$                  | —                       | —             | 150                     | uA     |

| I <sub>BHLH</sub>                             | Bus Hold High Overdrive Current                                                  | $0 \le V_{IN} \le V_{IH} (MAX)$                  | —                       | —             | 150                     | uA     |

| V <sub>BHT</sub>                              | Bus Hold Trip Points                                                             | $0 \le V_{IN} \le V_{IH} (MAX)$                  | V <sub>CCO</sub> * 0.35 | —             | V <sub>CCO</sub> * 0.65 | uA     |

| C1                                            | 1/O Canacitanaa <sup>1</sup>                                                     | V <sub>CCO</sub> = 3.3V, 2.5V, 1.8V              | —                       | 8             | —                       | pf     |

| CT.                                           | I/O Capacitance <sup>1</sup>                                                     | $V_{CC}$ = 1.8V, $V_{IO}$ = 0 to $V_{IH}$ (MAX)  | —                       |               | —                       |        |

| C2                                            | Clock Conseitones                                                                | V <sub>CCO</sub> = 3.3V, 2.5V, 1.8V              | —                       | 6             | —                       | pf     |

| 02                                            | Clock Capacitance <sup>1</sup>                                                   | $V_{CC}$ = 1.8V, $V_{IO}$ = 0 to $V_{IH}$ (MAX)  | —                       |               | -                       |        |

| C3                                            | Clobal Input Capacitanaa <sup>1</sup>                                            | V <sub>CCO</sub> = 3.3V, 2.5V, 1.8V              | —                       | 6             | —                       | pf     |

| 03                                            | Global Input Capacitance <sup>1</sup>                                            | $V_{CC} = 1.8$ V, $V_{IO} = 0$ to $V_{IH}$ (MAX) | —                       |               | —                       |        |

| I <sub>OSD</sub>                              | Output Short Circuit Current                                                     | V <sub>OD</sub> = 0V Driver Output Shorted       | —                       | _             | 24                      | mA     |

| with the                                      | I/O leakage current is measured with the output driver active. Bus maintenance c |                                                  | with the output         | driver trista | ated. It is not me      | asured |

### **Over Recommended Operating Conditions**

2. T<sub>A</sub> 25°C, f=1.0MHz

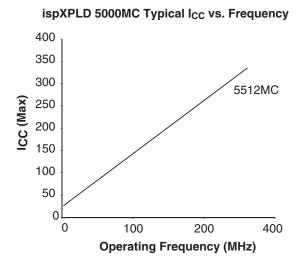

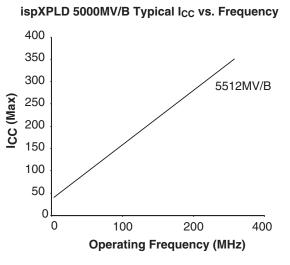

### Supply Current

| Symbol                          | Parameter                                   | Condition                                  | Min | Typ <sup>3</sup> | Max | Units |

|---------------------------------|---------------------------------------------|--------------------------------------------|-----|------------------|-----|-------|

| ispXPLD                         | 5512                                        |                                            |     | 1 1              |     | Į.    |

|                                 |                                             | V <sub>CC</sub> = 3.3V, f = 1.0MHz         | —   |                  | _   | mA    |

| I <sub>CC</sub> <sup>1, 2</sup> | Operating Power Supply Current              | V <sub>CC</sub> = 2.5V, f = 1.0MHz         | _   |                  | _   | mA    |

|                                 |                                             | V <sub>CC</sub> = 1.8V, f = 1.0MHz         | —   |                  | _   | mA    |

|                                 |                                             | V <sub>CC</sub> = 3.3V, f = 0MHz, unloaded | _   |                  | _   | mA    |

| I <sub>CCO</sub>                | Standby Power Supply Current (per I/O Bank) | $V_{CC}$ = 2.5V, f = 0MHz, unloaded        | _   |                  | _   | mA    |

|                                 |                                             | V <sub>CC</sub> = 1.8V, f = 0MHz, unloaded | —   |                  | _   | mA    |

|                                 |                                             | V <sub>CC</sub> = 3.3V, f = 10MHz          | _   |                  | _   | mA    |

| I <sub>CCOP</sub>               | PLL Power Supply Current<br>(per PLL Bank)  | V <sub>CC</sub> = 2.5V, f = 10MHz          | _   |                  | _   | mA    |

|                                 |                                             | V <sub>CC</sub> = 1.8V, f = 10MHz          | _   |                  | _   | mA    |

1. Device configured with 16-bit counters.

2. ICC varies with specific device configuration and operating frequency.

3.  $T_A = 25^{\circ}C$

# sysIO Recommended Operating Conditions

|                   |      | V <sub>CCO</sub> (V) <sup>2</sup> |      |       | V <sub>REF</sub> (V) |       |

|-------------------|------|-----------------------------------|------|-------|----------------------|-------|

| Standard          | Min. | Тур.                              | Max. | Min.  | Тур.                 | Max.  |

| LVCMOS 3.3        | 3.0  | 3.3                               | 3.6  | _     | _                    | _     |

| LVCMOS 2.5        | 2.3  | 2.5                               | 2.7  | _     | -                    | —     |

| LVCMOS 1.81       | 1.65 | 1.8                               | 1.95 | -     | -                    | —     |

| LVTTL             | 3.0  | 3.3                               | 3.6  | _     | _                    | _     |

| PCI 3.3           | 3.0  | 3.3                               | 3.6  | _     | -                    | —     |

| PCI-X             | 3.0  | 3.3                               | 3.6  | _     | —                    | _     |

| AGP-1X            | 3.15 | 3.3                               | 3.45 | _     | -                    | _     |

| SSTL 2            | 2.3  | 2.5                               | 2.7  | 1.15  | 1.25                 | 1.35  |

| SSTL 3            | 3.0  | 3.3                               | 3.6  | 1.3   | 1.5                  | 1.7   |

| CTT 3.3           | 3.0  | 3.3                               | 3.6  | 1.35  | 1.5                  | 1.65  |

| CTT 2.5           | 2.3  | 2.5                               | 2.7  | 1.35  | 1.5                  | 1.65  |

| HSTL Class I      | 1.4  | 1.5                               | 1.6  | 0.68  | 0.75                 | 0.9   |

| HSTL Class III    | 1.4  | 1.5                               | 1.6  | _     | 0.9                  | _     |

| HSTL Class IV     | 1.4  | 1.5                               | 1.6  | -     | 0.9                  | _     |

| GTL+              | 1.4  | -                                 | 3.6  | 0.882 | 1.0                  | 1.122 |

| LVDS <sup>3</sup> | 2.3  | 2.5                               | 3.6  | -     | _                    | —     |

Design tools default setting.

Inputs are independent of V<sub>CCO</sub> setting. However, V<sub>CCO</sub> must be set within the valid operating range for one of the supported standards.

### sysIO Single Ended DC Electrical Characteristics

| Input/Output               | ١       | / <sub>IL</sub>         | V                       | IH      | V <sub>OL</sub>        | V <sub>OH</sub>         | I <sub>OL</sub> <sup>2</sup> | I <sub>OH</sub> <sup>2</sup>    |

|----------------------------|---------|-------------------------|-------------------------|---------|------------------------|-------------------------|------------------------------|---------------------------------|

| Standard                   | Min (V) | Max (V)                 | Min (V)                 | Max (V) | Max (V)                | Min (V)                 | (mA)                         | (mA)                            |

| LVCMOS 3.3                 | -0.3    | 0.8                     | 2.0                     | 3.6     | 0.4                    | 2.4                     | 20, 16, 12,<br>8, 5.33, 4    | -20, -16, -12,<br>-8, -5.33, -4 |

|                            |         |                         |                         |         | 0.2                    | V <sub>CCO</sub> - 0.2  | 0.1                          | -0.1                            |

| LVTTL                      | -0.3    | 0.8                     | 2.0                     | 3.6     | 0.4                    | 2.4                     | 4                            | -4                              |

|                            | -0.5    | 0.8                     | 2.0                     | 3.0     | 0.2                    | V <sub>CCO</sub> - 0.2  | 0.1                          | -0.1                            |

| LVCMOS 2.5                 | -0.3    | 0.7                     | 1.7                     | 3.6     | 0.4                    | V <sub>CCO</sub> - 0.4  | 16, 12, 8,<br>5.33, 4        | -16, -12, -8,<br>-5.33, -4      |

|                            |         |                         |                         |         | 0.2                    | V <sub>CCO</sub> - 0.2  | 0.1                          | -0.1                            |

| LVCMOS 1.8 <sup>1, 3</sup> | -0.3    | 0.68                    | 1.07                    | 3.6     | 0.4                    | V <sub>CCO</sub> - 0.4  | 8                            | -8                              |

| LVCMOS 1.83                | -0.3    | 0.68                    | 1.07                    | 3.6     | 0.4                    | V <sub>CCO</sub> -0.4   | 12, 5.33, 4                  | -12, -5.33, -4                  |

|                            | -0.3    | 0.00                    | 1.07                    | 3.0     | 0.2                    | V <sub>CCO</sub> - 0.2  | 0.1                          | -0.1                            |

| PCI 3.34                   | -0.3    | 1.08                    | 1.5                     | 3.6     | 0.1 V <sub>CCO</sub>   | 0.9 V <sub>CCO</sub>    | 1.5                          | -0.5                            |

| PCI -X <sup>5</sup>        | -0.3    | 1.26                    | 1.5                     | 3.6     | 0.1 V <sub>CCO</sub>   | 0.9 V <sub>CCO</sub>    | 1.5                          | -0.5                            |

| AGP-1X⁴                    | -0.3    | 1.08                    | 1.5                     | 3.6     | 0.1 V <sub>CCO</sub>   | 0.9 V <sub>CCO</sub>    | 1.5                          | -0.5                            |

| SSTL3 class I              | -0.3    | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 3.6     | 0.7                    | V <sub>CCO</sub> - 1.1  | 8                            | -8                              |

| SSTL3 class II             | -0.3    | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 3.6     | 0.5                    | V <sub>CCO</sub> - 0.9  | 16                           | -16                             |

| SSTL2 class I              | -0.3    | V <sub>REF</sub> - 0.18 | V <sub>REF</sub> + 0.18 | 3.6     | 0.54                   | V <sub>CCO</sub> - 0.62 | 7.6                          | -7.6                            |

| SSTL2 class II             | -0.3    | V <sub>REF</sub> - 0.18 | V <sub>REF</sub> + 0.18 | 3.6     | 0.35                   | V <sub>CCO</sub> - 0.43 | 15.2                         | -15.2                           |

| CTT 3.3                    | -0.3    | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 3.6     | V <sub>REF</sub> - 0.4 | V <sub>REF</sub> + 0.4  | 8                            | -8                              |

| CTT 2.5                    | -0.3    | V <sub>REF</sub> - 0.3  | V <sub>REF</sub> + 0.2  | 3.6     | V <sub>REF</sub> - 0.4 | V <sub>REF</sub> + 0.4  | 8                            | -8                              |

| HSTL class I               | -0.3    | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | 3.6     | 0.4                    | V <sub>CCO</sub> - 0.4  | 8                            | -8                              |

| HSTL class III             | -0.3    | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.1  | 3.6     | 0.4                    | V <sub>CCO</sub> - 0.4  | 24                           | -8                              |

| HSTL class IV              | -0.3    | V <sub>REF</sub> - 0.3  | V <sub>REF</sub> + 0.1  | 3.6     | 0.4                    | V <sub>CCO</sub> - 0.4  | 48                           | -8                              |

| GTL+                       | -0.3    | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 3.6     | 0.6                    | n/a                     | 36                           | n/a                             |

**Over Recommended Operating Conditions**

1. Software default setting.

2. The average DC current drawn by I/Os between adjacent bank GND connections, or between the last GND in an I/O bank and the end of the I/O bank, as shown in the logic signals connection table, shall not exceed n\*8mA. Where n is the number of I/Os between bank GND connections or between the last GND in a bank and the end of a bank.

3. For 1.8V devices (ispXPLD 5000MC) these specifications are  $V_{IL} = 0.35 * V_{CC}$  and  $V_{IH} = 0.65 * V_{CC}$ 4. For 1.8V devices (ispXPLD 5000MC) these specifications are  $V_{IL} = 0.3 * V_{CC} * 3.3/1.8$ ,  $V_{IH} = 0.5 * V_{CC} * 3.3/1.8$ 5. For 1.8V devices (ispXPLD 5000MC) these specifications are  $V_{IL} = 0.35 * V_{CC} * 3.3/1.8$  and  $V_{IH} = 0.5 * V_{CC} * 3.3/1.8$

# sysIO Differential DC Electrical Characteristics

| Parameter                           | Description                                    | Test Condtions                                                 | Min.     | Тур.  | Max.    |

|-------------------------------------|------------------------------------------------|----------------------------------------------------------------|----------|-------|---------|

| LVDS                                | 1                                              | -                                                              |          |       | 1       |

| V <sub>INP</sub> . V <sub>INP</sub> | Input Voltage                                  |                                                                | 0V       | —     | 2.4V    |

| V <sub>THD</sub>                    | Differential Input Threshold                   |                                                                | +/-100mV | _     | _       |

| V <sub>CM</sub>                     | Input Common Mode Voltage                      | Half the sum of the two inputs                                 | 0.05V    | _     | 2.35V   |

| I <sub>IN</sub>                     | Input Current                                  | Power On or Power Off                                          | _        | _     | +/-10uA |

| V <sub>OH</sub>                     | Output High Voltage for $V_{OP}$ or $V_{OM}$   | RT = 100 Ohm                                                   | _        | 1.38V | 1.60V   |

| V <sub>OL</sub>                     | Output Low Voltage for $V_{OP}$ or $V_{OM}$    | RT = 100 Ohm                                                   | 0.9V     | 1.03V | _       |

| V <sub>OD</sub>                     | Output Voltage Differential                    | (V <sub>OP</sub> - V <sub>OM</sub> ), R <sub>T</sub> = 100 Ohm | 250mV    | 350mV | 450mV   |

| $\Delta V_{OD}$                     | Change in V <sub>OD</sub> Between High and Low |                                                                | _        | _     | 50mV    |

| V <sub>OS</sub>                     | Output Voltage Offset                          | $(V_{OP} - V_{OM})/2, R_T = 100 \text{ Ohm}$                   | 1.125V   | 1.20V | 1.375V  |

| ΔV <sub>OS</sub>                    | Change in V <sub>OS</sub> Between H and L      |                                                                | —        | —     | 50mV    |

| I <sub>OSD</sub>                    | Output Short Circuit Current                   | V <sub>OD</sub> = 0V Driver outputs<br>shorted                 | -        | _     | 24mA    |

### **Over Recommended Operating Conditions**

# ispXPLD 5512MX External Switching Characteristics<sup>1, 2, 3</sup>

|                               |                                                                                                | -    | 4    | -    | 5    | -7   | 75   | -10  |      |       |

|-------------------------------|------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|-------|

| Parameter                     | Description                                                                                    | Min. | Max. | Min. | Max. | Min. | Max. | Min. | Max. | Units |

| t <sub>PD</sub>               | Data propagation delay, 5-PT bypass                                                            | -    | 4.0  | _    | 5.0  | _    | 7.5  | _    | 10.0 | ns    |

| t <sub>PD_PTSA</sub>          | Data propagation delay                                                                         | -    | 5.7  | _    | 7.1  | _    | 10.7 | _    | 14.3 | ns    |

| t <sub>S</sub>                | GLB register setup time before clock, 5-PT bypass                                              | 2.9  | -    | 3.6  | -    | 5.4  | -    | 7.3  | -    | ns    |

| t <sub>S_PTSA</sub>           | GLB register setup time before clock                                                           | -    | _    | —    | _    | _    | —    | _    | _    | ns    |

| t <sub>SIR</sub>              | GLB register setup time before clock, input register path                                      | 2.0  | -    | 2.5  | -    | 3.8  | _    | 5.0  | -    | ns    |

| t <sub>H</sub>                | GLB register hold time before clock,<br>5-Ptbypass                                             | 0.0  | -    | 0.0  | -    | 0.0  | _    | 0.0  | -    | ns    |

| t <sub>H_PTSA</sub>           | GLB register hold time before clock                                                            | -    | _    | -    | -    | -    | -    | _    | -    | ns    |

| t <sub>HIR</sub>              | GLB register hold time before clock, input register path                                       | 0.0  | -    | 0.0  | -    | 0.0  | _    | 0.0  | -    | ns    |

| t <sub>CO</sub>               | GLB register clock-to-output delay                                                             | -    | 3.0  | —    | 3.8  | _    | 5.6  | _    | 7.5  | ns    |

| t <sub>R</sub>                | External reset pin to output delay                                                             | -    | 4.5  | -    | 5.6  | -    | 8.4  | —    | 11.3 | ns    |

| t <sub>RW</sub>               | Reset pulse duration                                                                           | 1.8  | _    | 2.3  | -    | 3.4  | -    | 4.5  | -    | ns    |

| t <sub>LPTOE/DIS</sub>        | Input to output local product term output enable/disable                                       | -    | 6.0  | _    | 7.5  | _    | 11.3 | _    | 15.0 | ns    |

| t <sub>SPTOE/DIS</sub>        | Input to output shared product term output enable/disable                                      | -    | 6.0  | _    | 7.5  | _    | 11.3 | _    | 15.0 | ns    |

| t <sub>GOE/DIS</sub>          | Global OE input to output enable/disable                                                       | -    | 4.2  | —    | 5.3  | _    | 7.9  | _    | 10.5 | ns    |

| t <sub>CW</sub>               | Clock width, high or low                                                                       | 1.7  | -    | 2.1  | -    | 3.2  | -    | 4.3  | -    | ns    |

| t <sub>GW</sub>               | Gate width low (for low transparent) or high (for high transparent)                            | 1.7  | -    | 2.1  | -    | 3.2  | _    | 4.3  | -    | ns    |

| t <sub>WIR</sub>              | Input register clock width, high or low                                                        | 1.7  | —    | 2.1  | -    | 3.2  | -    | 4.3  | -    | ns    |

| t <sub>SKEW</sub>             | Clock-to-out skew, block level                                                                 | -    | 0.6  | —    | 0.8  | _    | 1.1  | —    | 1.5  | ns    |

| f <sub>MAX</sub> <sup>4</sup> | Clock frequency with internal feedback                                                         | -    | 250  | _    | 200  | _    | 133  | _    | 100  | MHz   |

| f <sub>MAX</sub> (Ext.)       | Clock frequency with external feedback, $1/(t_{S_PTSA} + t_{CO})$                              | -    | -    | _    | _    | _    | _    | _    | -    | MHz   |

| f <sub>MAX</sub> (Tog.)       | Clock frequency max toggle                                                                     | -    | 333  | —    | 266  | _    | 177  | —    | 133  | MHz   |

| f <sub>MAX</sub> (CAMC)       | Clock frequency to CAM (configure mode)                                                        | -    | -    | —    | -    | —    | -    | —    | -    | MHz   |

| f <sub>MAX</sub> (CAM)        | Clock frequency to CAM (compare mode)                                                          | -    | -    | -    | -    | -    | -    | _    | -    | MHz   |

| f <sub>MAX</sub> (RAM)        | Clock frequency to RAM in<br>- Single port Mode<br>- Dual port Mode<br>- Pseudo dual port Mode | -    | -    | _    | -    | —    | —    | —    | _    | MHz   |

| t <sub>PWR_ON</sub>           | Power-on Time                                                                                  | -    | _    | _    | -    | _    | _    | _    | —    | uS    |

#### **Over Recommended Operating Conditions**

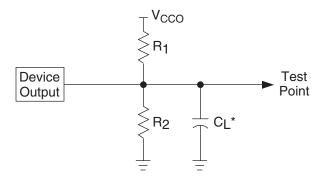

1. Timing numbers are based on default LVCMOS 1.8 I/O buffers. Use timing adjusters provided to calculate timing for other standards.

2. Measured using standard switching circuit, global routing loading of 1, worst case PTSA loading and 1 output switching.

3. Pulse widths and clock widths less than minimum will cause unknown behavior.

4. Standard 16-bit counter using SRP feedback.

### **Timing Model**

The task of determining timing in a ispXPLD 5000MX device is relatively simple. The timing model show in Figure 18 shows the specific delay paths. Once the implementation of a given function is determined either conceptually of from the software report file, the delay path of a function can easily be determined from the timing model. The Lattice design tools report the timing delays based on the same timing model. Note that internal timing parameters are for reference only, and are not tested. The external timing parameters are tested and guaranteed for every device.

#### Figure 18. ispXPLD 5000MX Timing Model Diagram

# sysCLOCK PLL Timing

| Symbol                          | Parameter                                     | Conditions                                                                                                | Min      | Max      | Units |

|---------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------|----------|-------|

| t <sub>PWH</sub>                | Input clock, high time                        | 80% to 80%                                                                                                | 0.5      | _        | ns    |

| t <sub>PWL</sub>                | Input clock, low time                         | 20 % to 20%                                                                                               | 0.5      | —        | ns    |

| t <sub>R</sub> , t <sub>F</sub> | Input Clock, rise and fall time               | 20% to 80%                                                                                                | -        | 3.0      | ns    |

| t <sub>INSTB</sub>              | Input clock stability, cycle to cycle (peak)  |                                                                                                           | -        | +/- 300  | ps    |

| f <sub>MDIVIN</sub>             | M Divider input, frequency range              |                                                                                                           | 10       | 320      | MHz   |

| f <sub>MDIVOUT</sub>            | M Divider output, frequency range             |                                                                                                           | 10       | 320      | MHz   |

| f <sub>NDIVIN</sub>             | N Divider input, frequency range              |                                                                                                           | 10       | 320      | MHz   |

| f <sub>NDIVOUT</sub>            | N Divider output, frequency range             |                                                                                                           | 10       | 320      | MHz   |

| f <sub>VDIVIN</sub>             | V Divider input, frequency range              |                                                                                                           | 100      | 400      | MHz   |